I. Introduction▲

Apprenez à acquérir et à contrôler des E/S FPGA et à simuler votre diagramme de manière fonctionnelle depuis votre ordinateur de développement avant de le compiler pour l'exécuter comme un circuit matériel. Cet exemple de projet a pour but d'effectuer des mesures DC de données analogiques.

II. Démarrer un nouveau projet CompactRIO dans LabVIEW▲

Suivez ce tutoriel ou téléchargez l'exemple de code ci-joint et ouvrez le projet DC and RMS Measurement.lvproj pour explorer le code en suivant les étapes ci-dessous.

Créez tout d'abord un nouveau projet LabVIEW pour gérer votre code et les ressources matérielles.

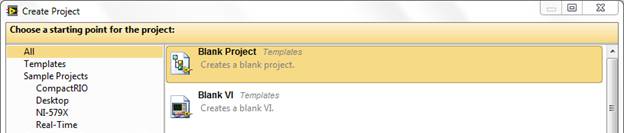

1. Créez un nouveau projet LabVIEW en sélectionnant Fichier » Créer un projet. Sélectionnez ensuite un Projet vide.

2. L'arborescence du projet par défaut contient le Poste de travail, où vous pouvez développer du code qui s'exécutera sur la machine Windows sur laquelle vous travaillez actuellement. Notez qu'une cible temps réel dispose d'un processeur qui exécute un système d'exploitation temps réel ; il s'agit donc d'un ordinateur à part entière. Pour développer du code qui s'exécutera sur cet ordinateur, vous devez ajouter une nouvelle cible à votre projet. Cliquez avec le bouton droit sur l'élément Projet au sommet de l'arborescence et sélectionnez Nouveau » Cibles et périphériques… pour ajouter un système temps réel au projet.

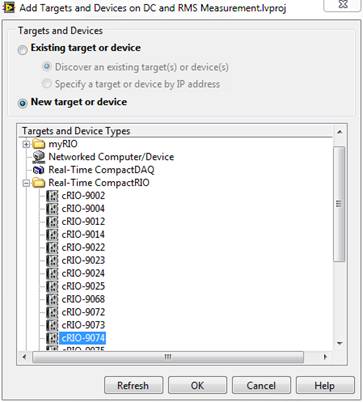

3. Dans la boîte de dialogue, vous pouvez visualiser les systèmes déjà présents dans votre réseau ou en ajouter un nouveau. Sélectionnez Nouvelle cible ou nouveau périphérique. LabVIEW répertorie les périphériques disponibles en fonction des pilotes installés. Étant donné que vous avez installé le pilote NI-RIO avec votre logiciel d'évaluation, sélectionnez et développez l'élément Real-Time CompactRIO, puis sélectionnez cRIO-9074.

4. Enregistrez le projet en cliquant sur Fichier » Enregistrer et nommez-le DC and RMS Measurement. Cliquez sur OK.

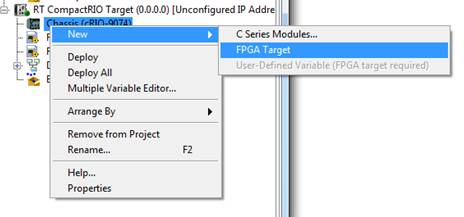

5. Cliquez avec le bouton droit sur l'élément Chassis, qui désigne la face-arrière de la cible CompactRIO, et sélectionnez Nouveau » FPGA Target. Cela place la cible Compact RIO en mode Interface FPGA, ce qui vous permet d'acquérir des E/S à partir d'une application FPGA.

6. Si un système existe au préalable, LabVIEW essaiera de détecter les E/S présentes et de les ajouter automatiquement au projet LabVIEW. Étant donné que vous avez ajouté un nouveau système, vous devez ajouter manuellement un module d'E/S de la Série C. Pour ce faire, cliquez avec le bouton droit sur le nouvel élément FPGA Target et sélectionnez Nouveau » C Series Modules…

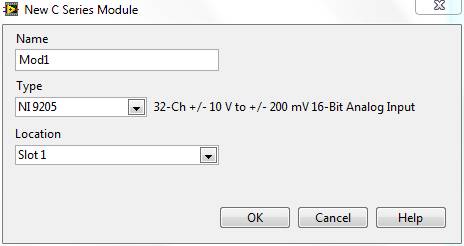

7. Comme pour la cible précédente, étant donné que vous n'avez pas de matériel physique, sélectionnez Nouvelle cible ou nouveau périphérique. Sélectionnez ensuite C Series Module et cliquez sur OK.

8. Dans la boîte de dialogue qui s'affiche, sélectionnez un module d'entrée analogique NI 9205 comme Mod1 puis cliquez sur OK.

III. Créer une application FPGA▲

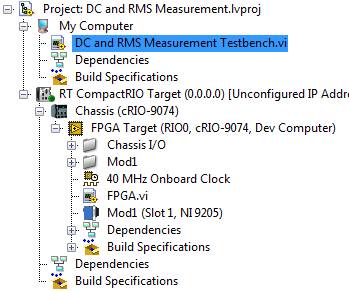

1. Vous devriez à présent avoir un nouveau projet LabVIEW qui contient votre système CompactRIO, ainsi qu'un contrôleur, un châssis, un FPGA et des modules d'E/S de la Série C. Bien que, dans le cadre de ce tutoriel, vous utilisiez un module d'entrée analogique NI 9205, le même procédé s'applique pour n'importe quel module d'entrée analogique.

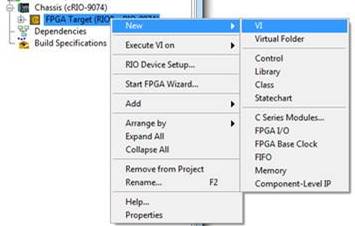

2. Dans le projet LabVIEW, développez l'arborescence du contrôleur et du châssis CompactRIO temps réel pour afficher l'élément FPGA. Faites un clic droit sur l'élément FPGA et sélectionnez Nouveau » VI. Ce VI effectue l'acquisition de données analogiques et le traitement de signaux haute vitesse.

3. Enregistrez le VI sous le nom FPGA.vi.

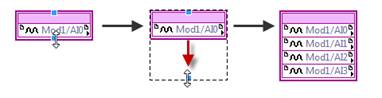

4. Pour ajouter un nœud d'E/S dans le but d'acquérir un échantillon à partir du module d'entrée analogique, développez le dossier Mod1 et glissez l'élément Mod1/AI0 dans le diagramme du VI FPGA.

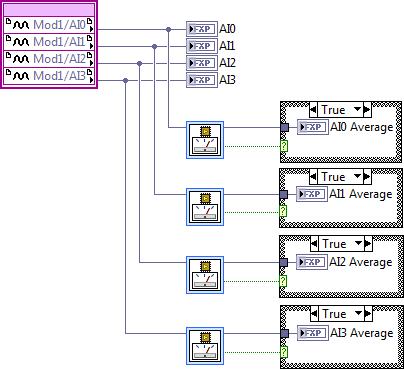

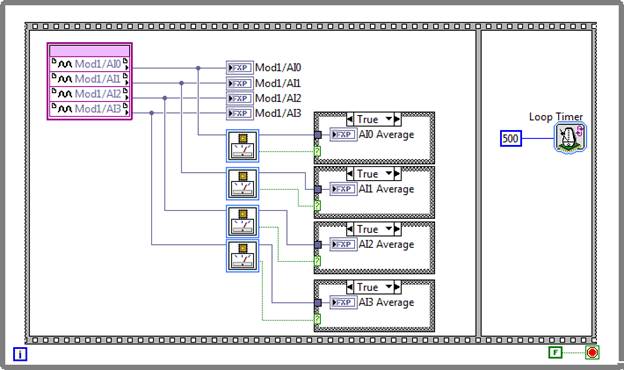

5. Étendez le nœud d'E/S en cliquant et en étirant le bord inférieur, comme le montre l'image ci-dessous, afin de faire apparaître les voies AI0 à AI3. Ainsi, le nœud d'E/S échantillonne les quatre voies à chaque nouvelle exécution.

6. Créez un indicateur pour chaque voie d'entrée analogique.

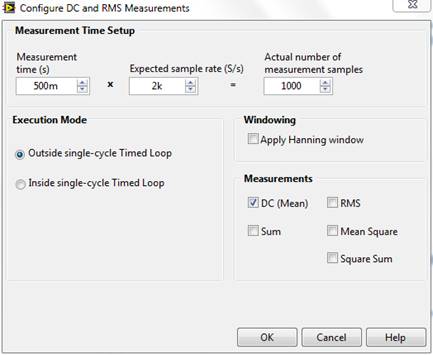

7. Déposez quatre instances du VI DC and RMS Measurements dans le diagramme et configurez-les pour une mesure DC, calculée toutes les 500 ms avec une fréquence d'acquisition de 2 kS/s. De cette manière, le VI calculera la valeur moyenne des échantillons d'entrée à chaque fois qu'un ensemble de données de 1000 échantillons sera acquis.

8. La fonction DC and RMS Measurement renvoie une valeur Vrai pour la sortie output valid? chaque fois qu'une moyenne est calculée et renvoyée (lorsqu'un ensemble de données de 1000 échantillons a été acquis). Déposez quatre structures Condition dans le diagramme, créez des indicateurs pour chaque sortie DC result et utilisez la sortie booléenne output valid? pour contrôler la structure Condition comme le montre l'image ci-dessous. Cela met les indicateurs à jour lorsqu'un résultat valide est disponible.

9. Enfermez le code développé jusqu'ici dans une structure Séquence déroulée et ajoutez une étape après le code. Placez un VI Loop Timer (cadencement de boucle) dans le second cadre et configurez le compteur en μSec. Câblez une constante de valeur 500 au Loop Timer. Enfin, placez une boucle While autour de la structure Séquence déroulée et créez une constante Faux pour sa condition d'arrêt.

IV. Découvrir le banc de test du bureau pour la simulation FPGA▲

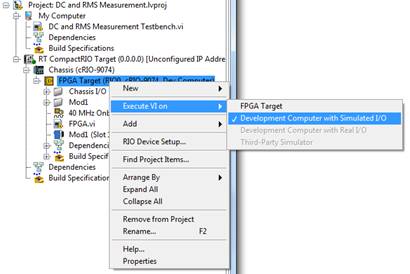

1. Lorsque vous développez un VI LabVIEW FPGA, il est conseillé de simuler votre conception avant de la compiler sur matériel. Cela vous permet de gagner du temps de développement, de vous assurer de la bonne implémentation de la logique et d'effectuer rapidement des opérations itératives sur vos conceptions. Pour exécuter votre code dans le cadre d'une simulation, cliquez avec le bouton droit sur l'élément FPGA Target et sélectionnez Select Execution Mode » Simulation (Simulated I/O).

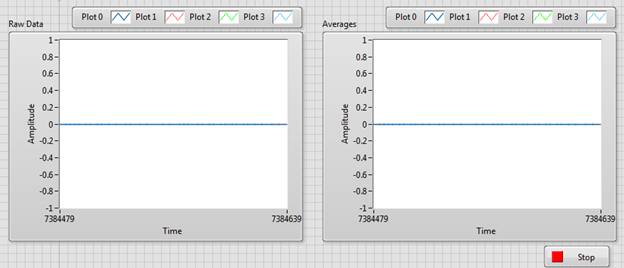

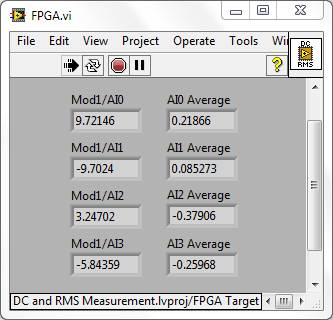

2. Cliquez sur la flèche Exécuter pour lancer le code et visualiser les mesures DC et RMS effectuées au niveau d'E/S aléatoires prises pour entrées par défaut.

3. Étant donné que vous êtes en train d'évaluer le produit et que vous ne disposez pas de matériel physique, votre conception est simulée. Faites un double-clic sur le VI DC and RMS Measurement Testbench.vi à partir de votre projet LabVIEW.

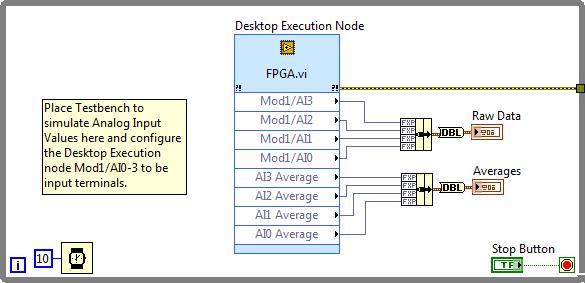

Vous remarquerez que le banc de test (Testbench) est situé sous l'arborescence du Poste de travail ; il s'exécute donc sur votre ordinateur de bureau, met en action les entrées dans la logique FPGA, et lit les sorties par l'intermédiaire du Desktop Execution Node (nœud d'exécution depuis le bureau). Étant donné que le VI du banc de test s'exécute dans un contexte hôte, vous disposez de centaines de fonctions que vous pouvez utiliser pour créer des vecteurs/cas/stimuli de test en plus de vérifier, d'analyser, d'afficher et de rapporter des résultats des tests.

4. Dans la face-avant, vous pouvez modifier les entrées qui seront envoyées à votre code FPGA et visualiser les résultats.

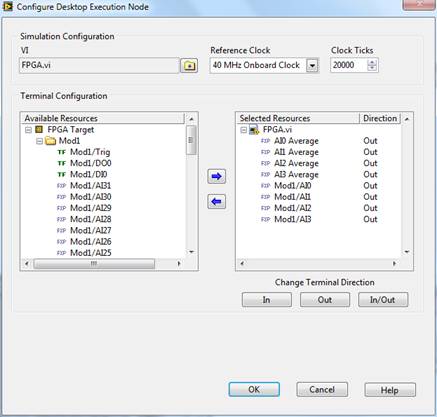

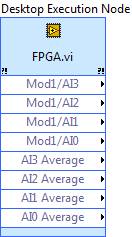

5. Appuyez sur < Ctrl-E > pour afficher le diagramme. Avec le Desktop Execution Node (nœud d'exécution depuis le bureau), vous pouvez vérifier les composants de votre logique FPGA. Cliquez avec le bouton droit sur le nœud et sélectionnez Configurer le nœud d'exécution de bureau…

6. Une fois que vous avez sélectionné votre VI FPGA, toutes les commandes, les indicateurs et les ressources FPGA auxquels vous avez accès apparaissent dans la fenêtre Available Resources. Vous pouvez configurer les terminaux du Desktop Execution Node en sélectionnant les ressources disponibles utiles et en vous servant des flèches bleues pour les transférer dans la fenêtre Selected Resources.

7. Les tops d'horloge (Clock ticks) correspondent à la valeur d'entrée des fonctions de cadencement de boucle (Loop Timer) du VI FPGA. Étant donné que le VI de cette application a été configuré en microsecondes, le nombre 20 000 correspond au résultat de la conversion suivante : 40 000 000 Hz * 500 µs. L'horloge FPGA embarquée par défaut utilisée ici est de 40 MHz.

8. Déposez votre banc de test pour simuler les valeurs d'entrées analogiques à l'endroit indiqué :

Si vous souhaitez compiler votre conception pour l'exécuter sur un matériel FPGA, vous devez installer les outils de compilation Xilinx. Dans l'arborescence du projet, mettez votre VI en mode d'exécution de matériel en cliquant avec le bouton droit sur FPGA Target puis en sélectionnant Select Execution Mode » FPGA Target. Pour commencer la compilation, cliquez simplement sur la flèche d'exécution dans votre VI LabVIEW FPGA.

LabVIEW vous invite alors à enregistrer votre VI, si vous ne l'avez pas déjà fait. LabVIEW entame ensuite le processus de transcription de votre diagramme FPGA en un langage de description matérielle natif et génère les fichiers nécessaires pour commencer la compilation. Cette opération peut être relativement longue. Remarque : Tout changement effectué sur le VI FPGA après cette opération devra faire l'objet d'une nouvelle compilation.

V. Ressources supplémentaires▲

Le type de données à virgule fixe LabVIEW.

Processus de compilation LabVIEW FPGA : De la flèche d'exécution au bitfile.

VI. Remerciements▲

Nous tenons à remercier Claude LeLoup pour la relecture et Zoom61 pour la mise au gabarit.